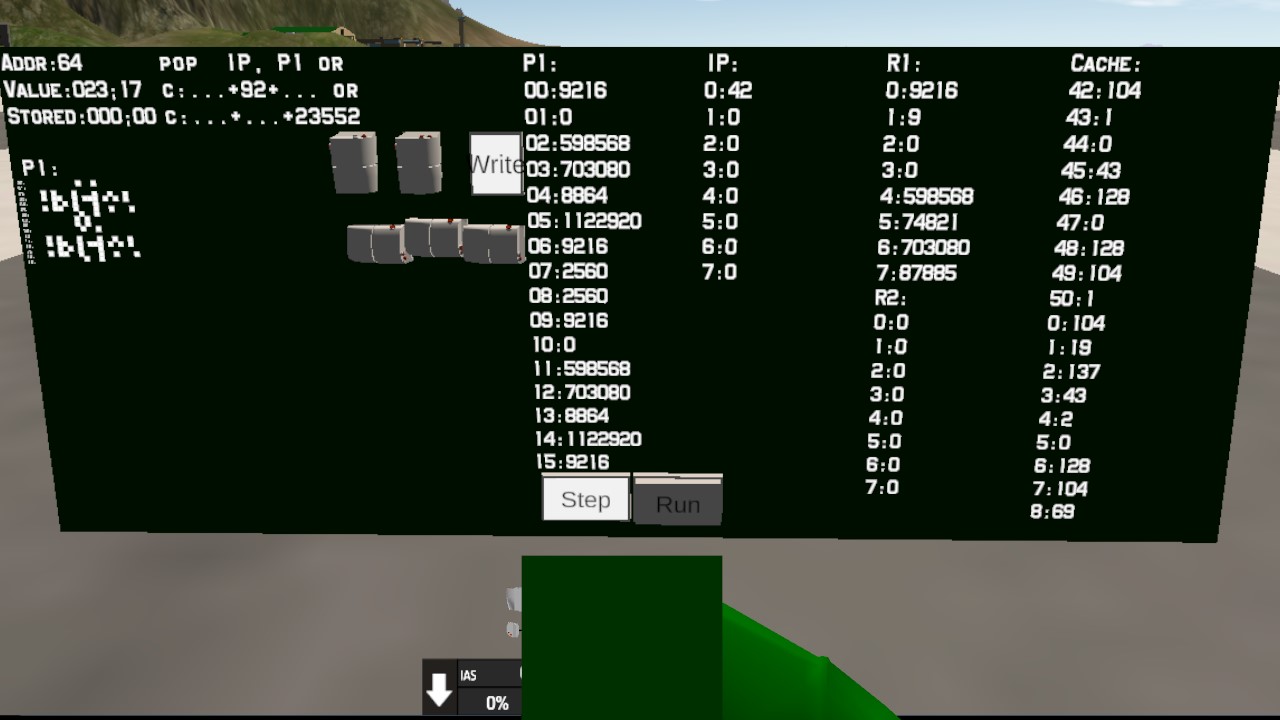

I'm not sure it works correctly but i hope so.

Clock rate:25?-800hz depending on physics settings;

Cache:9+9bytes;

RAM:512 bytes;

Registers:None. but there's four stacks, one of them is instruction pointer and one of them is used as display output.

Left side is for memory editor: two horizontal sliders are for value, three vertical ones are for address.

Address, value stored at that address (both decimal and hex) and value selected with sliders (both decimal and hex) are displayed in top-left corner of cube.

It will store value when you switch button, not while it's pressed.

There's a 24x16px screen near left edge of cube, it takes each value of P1 as a row and each of it's bits as a pixel, least significant ones are on the left edge.

On right side there's contents of stacks and cache and two buttons: AG1 executes one instruction when switched and AG2 executes instructions while it's on.

Instruction are either 8 or 24 bits long:

three least significant bits are for command;

fourth bit switches if second operand is in stack (off) or in memory (on)

fifth,sixth bits are for first operand (00:P1; 01:IP; 10:R1; 11:R2)

if fourth bit is off:seventh,eighth bits are for second operand; if it's same as for first operand, it will take second value from stack, not topmost one

if fourth bit is on:bits from seventh to last one is 18bit-long unsigned integer used as second operand.

Instructions:

0:pushes second operand to first one;

1:adds two operands and pushes result to first one (it will not remove first operand before pushing result)

2:subtraction

3:multiplication

4:division

5:if first operand is not equal to second, add 1 to topmost value of IP (IP is in bytes, not instructions)

6:if first operand is less than or equal to second, add 1 to topmost value of IP

7:pop first operand (doesn't cares about second operand)

One specific byte of memory can be used as instruction, middle part of it's operand or most significant part of it's operand, so there's three lines near top edge of block saying how it may work.

Values stored in stacks are floats, be careful not to make IP point to something.3333 bytes.

Cache is made from two parts:

First part stores 9 bytes from IP forwards;

Second part stores 9 bytes from last time IP jumped backwards.

Specifications

Spotlights

- MrCOPTY 10 months ago

- 32 1.2 years ago

- LettuceRob119 10 months ago

General Characteristics

- Predecessor 256-byte DDR RAM

- Created On Windows

- Wingspan 3.9ft (1.2m)

- Length 3.4ft (1.0m)

- Height 1.6ft (0.5m)

- Empty Weight 574lbs (260kg)

- Loaded Weight 574lbs (260kg)

Performance

- Wing Loading N/A

- Wing Area 0.0ft2 (0.0m2)

- Drag Points 385

Parts

- Number of Parts 12

- Control Surfaces 0

- Performance Cost 81

@11qazxc was wondering if it's possible or not in the 1st place

@MrCOPTY Maybe, but why?

Can u make a micro controller?

wow

i have summoned on this a very particular post

I like your funny words, magic man!

Not sure what's going on here but I support it!

@Stallia I agree

interesting

one of my classes rn has us building a ARM instruction processor + RAM from scratch with verilog and an fpga

cool stuff, ig whatever im doing would be pretty similar to this

There’s a lot of big boy words I can’t understand, but I think this is impressive